当嵌入式系统不再只是“控制器”,而成为一个可定义的智能单元,ZYNQ正告诉我们,未来的硬科技正在如何演化。

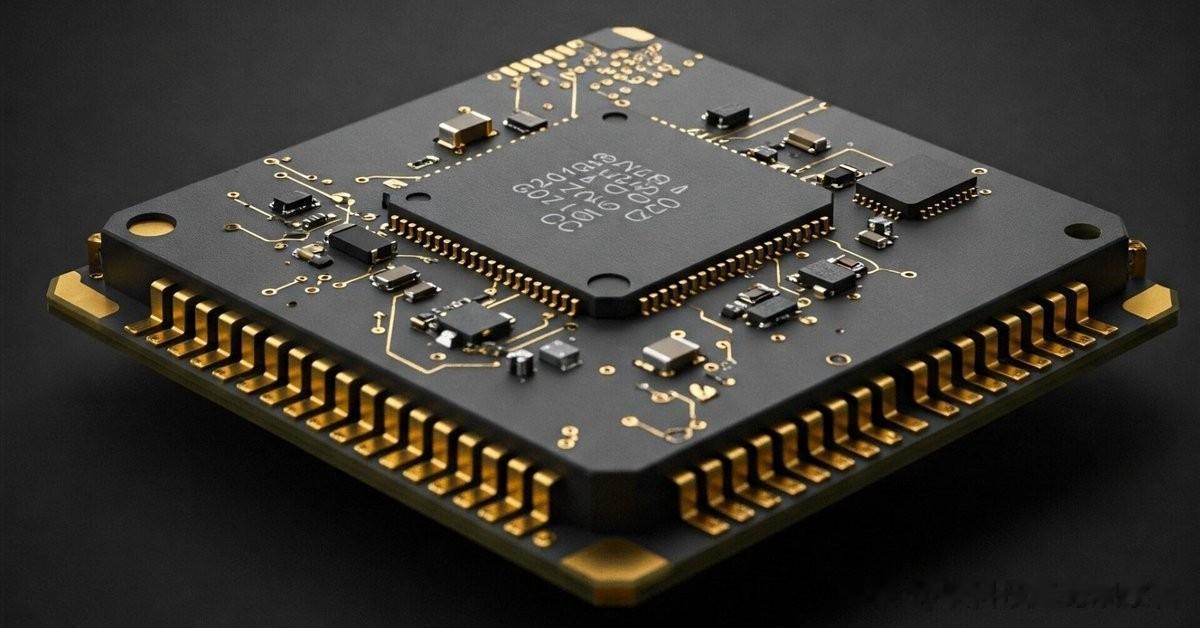

一、架构创新:ZYNQ为何重要在嵌入式系统的世界里,ZYNQ的意义早已超越了一颗芯片。它是软硬协同计算理念的开端——把 ARM Cortex-A9 双核处理系统(PS)与 FPGA 可编程逻辑(PL)集成在同一芯片中,实现了真正意义上的“系统级可定义”。

传统的嵌入式架构往往面临两难:

MCU 系统灵活但算力不足;FPGA 架构强大但开发复杂。而 ZYNQ 通过 AXI 总线将 ARM 与 FPGA 深度融合,让软件逻辑能动态调度硬件功能,让硬件逻辑能主动协同软件执行。这种“软硬融合式SoC”架构,代表了嵌入式设计从“可编程”迈向“可定义”的关键一步。

二、灵活互联:系统级设计的自由度革命

二、灵活互联:系统级设计的自由度革命ZYNQ 之所以受到工程师青睐,不仅因为算力,更因为它极高的互联灵活性。其 MIO(Multiplexed I/O)与 EMIO(Extended MIO)机制,使引脚资源能在 PS 与 PL 之间自由映射,从而实现真正意义上的硬件可重构。

这不仅简化了 PCB 布局、优化了 EMC 性能,更让设计者在系统层面上具备了“随需定义硬件”的能力。这正是当下Chiplet 模块化设计与异构计算架构的思想源头之一——未来的 SoC 将不再是静态设计,而是通过协议互联与逻辑编程实现动态重构的系统。

三、软硬协同:嵌入式智能的算力底座ZYNQ 的 PS-PL 融合架构在性能与实时性之间找到平衡。Cortex-A9 双核处理器提供了充足的操作系统支持(如 Linux/Android),而 PL 端 FPGA 逻辑则可承担高并行度、高带宽的实时任务,例如信号处理、图像识别或边缘AI计算。

通过 Vivado 工具链,工程师可用 C/C++、Python 级别的语言描述硬件行为,再由工具自动生成底层逻辑。这种从“电路逻辑”到“系统逻辑”的抽象层提升,使嵌入式系统进入了软件定义硬件(SDH)的新时代。

在工业控制、医疗影像、智能驾驶、边缘AI等场景中,ZYNQ式架构正成为现实可行的解决方案:高实时性、低延迟、低功耗、可重构——这正是未来嵌入式智能的四大关键词。

四、国产突围:从ZYNQ看中国SoC的未来路径ZYNQ的成功为中国嵌入式SoC提供了三点关键启示:

架构层突破:国产SoC必须走“异构算力”路线,实现 CPU、NPU、FPGA、DSP 的融合,而非简单叠加。当前寒武纪、芯动科技、平头哥等厂商正在探索类似“PS+PL”的复合架构。生态工具链:Vivado 的优势在于将复杂的FPGA开发流程软件化、可视化。国产EDA与IP生态要突围,必须构建统一的开发-验证-部署工具链体系。场景导向思维:ZYNQ的生命力在于场景适配。从工业控制到AI加速,不同型号覆盖不同层级市场。国产SoC若想脱颖而出,关键是在垂直场景中形成差异化算力优势,而非盲目追求通用性能。五、趋势判断:从“硬件定义系统”到“智能定义系统”ZYNQ代表的不是某一代FPGA技术,而是一种思维转变:

让硬件具备软件的可配置性,让算力具备智能的可定义性。

随着AI模型的边缘化与实时化需求持续增强,下一代SoC将走向“FPGA+AI加速器+高速互联+开放生态”的系统级融合架构。这意味着嵌入式系统的边界正在模糊——它不再只是“设备控制”,而是“智能协作”的算力节点。

结语|你怎么看?ZYNQ让嵌入式系统从“可编程”进入“可定义”时代,也让软硬协同计算真正落地。在国产化浪潮中,下一个ZYNQ式的突破,可能来自中国自己的架构创新。

关注我【硬科技趋势观察官】,每周深度拆解国产AI芯片、光模块与算力产业最新进展,用数据看趋势。

标签:#AI芯片 #算力 #国产替代 #嵌入式系统 #FPGA #硬科技趋势