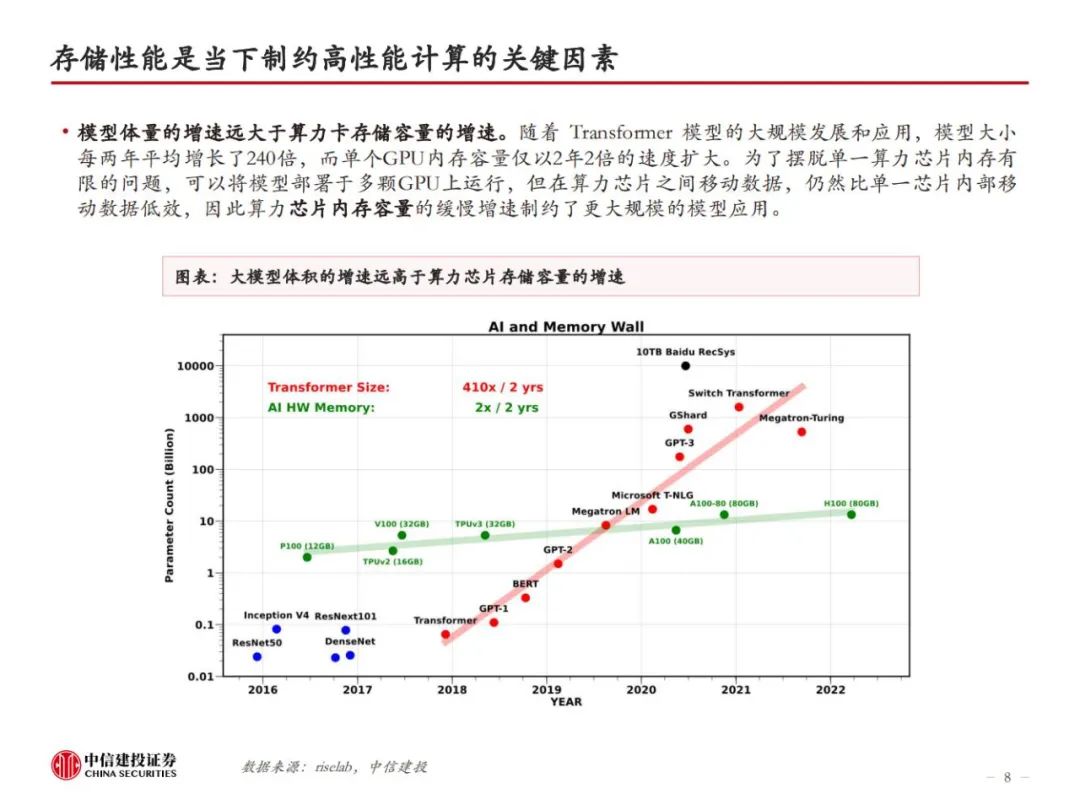

HBM现已成为算力提升的内存瓶颈。存储性能是高性能计算的核心制约,数据在存储器与处理器间传输时遭遇带宽和功耗瓶颈。为突破传统DRAM带宽局限,关键在于提升单I/O数据速率和位宽。HBM创新采用TSV、微凸块等技术,显著缩短信号传输路径,实现DRAM裸片与计算核心间的高效连接,具备高I/O数据速率、高位宽及低I/O电压特性,从而拥有了高带宽、高密度存储及低功耗等优势。然而,当前HBM的性能仍无法完全满足高端算力卡的需求。

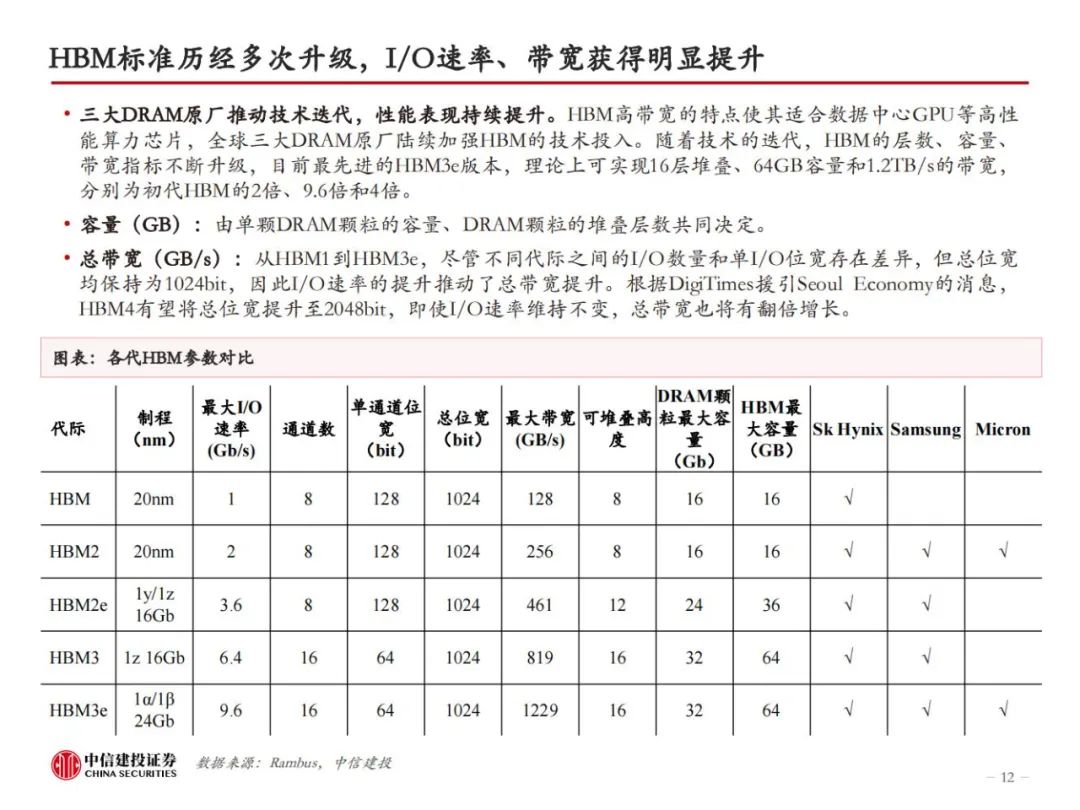

三大原厂持续加大研发投入,HBM性能倍数级提升。随着技术的迭代,HBM的层数、容量、带宽指标不断升级,目前最先进的HBM3e版本,理论上可实现16层堆叠、64GB容量和1.2TB/s的带宽,分别为初代HBM的2倍、9.6倍和4倍。从Trendforce公布的HBM Roadmap来看,2024年上半年,海力士、三星、美光均会推出24GB容量的HBM3e,均为8层堆叠。2024年下半年,三家厂商将推出36GB版本的HBM3e,或为12层堆叠。此外,HBM4有望于2026年推出。

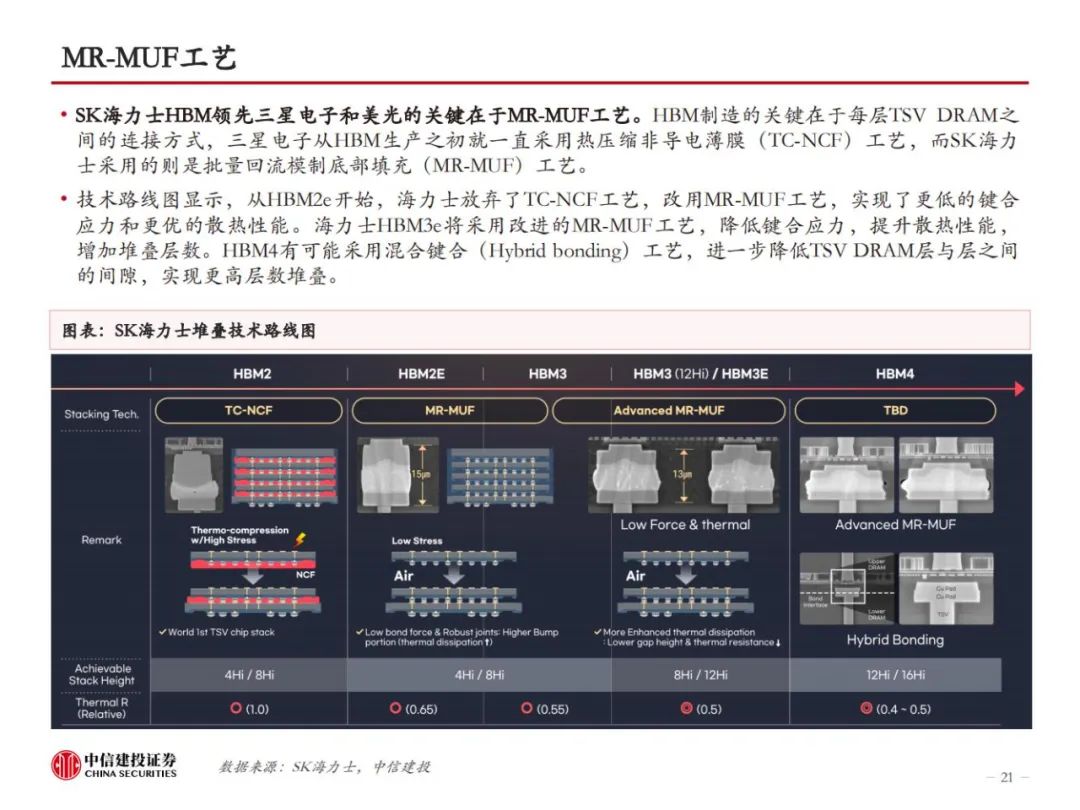

HBM制造集成前道工艺与先进封装,TSV、EMC、键合工艺是关键。HBM制造的关键在于TSV DRAM,以及每层TSV DRAM之间的连接方式。目前主流的HBM制造工艺是TSV+Micro bumping+TCB,例如三星的TC-NCF工艺,而SK海力士则采用改进的MR-MUF工艺,在键合应力、散热性能、堆叠层数方面更有优势。目前的TCB工艺可支撑最多16层的HBM生产,随着HBM堆叠层数增加,以及HBM对速率、散热等性能要求的提升,HBM4开始可能引入混合键合工艺,对应的,TSV、GMC/LMC的要求也将提高。

-对此,您有什么看法见解?-

-欢迎在评论区留言探讨和分享。-