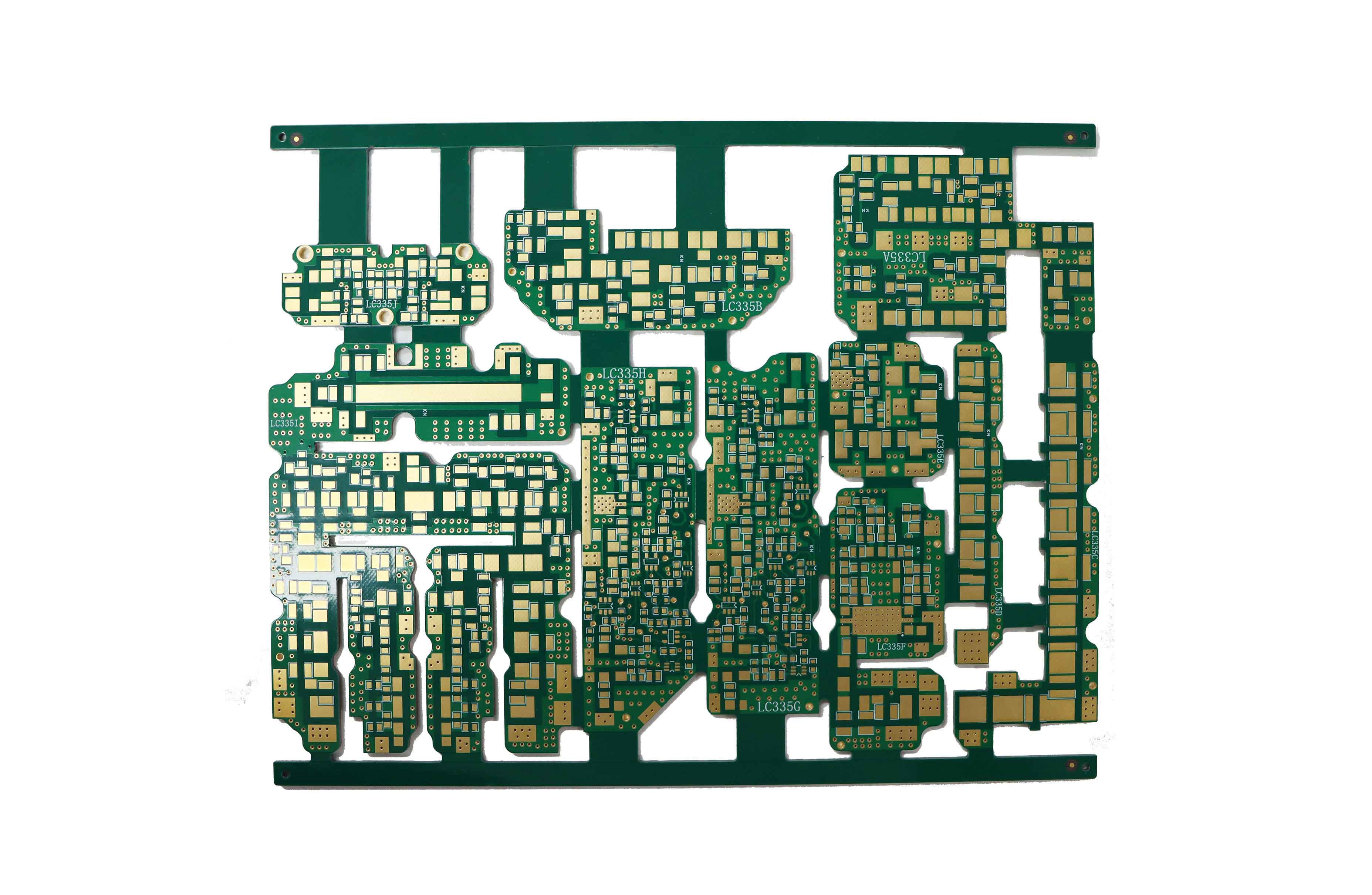

一站式PCBA加工厂家今天为大家讲讲高速PCB打样需要注意哪些事项?高速PCB打样需要注意事项。高速PCB打样是验证高速电路设计可行性与可靠性的关键环节,需从设计、材料、工艺、测试等多方面严格把控,以下是具体注意事项:

高速PCB打样需要注意事项

一、设计阶段:确保信号完整性与电磁兼容性

布局规划

关键信号优先:将高速信号(如时钟、差分对、高频信号)优先布局在内层,减少辐射干扰。

分区布局:按功能模块划分区域(如数字区、模拟区、电源区),避免信号交叉干扰。

散热设计:高功耗元件(如FPGA、电源芯片)集中布局,预留散热空间或增加散热焊盘。

布线规则

线宽与间距:根据信号频率调整线宽(如50Ω阻抗控制),保持最小间距(通常≥3倍线宽)。

避免直角/锐角:采用45°或圆弧转角,减少信号反射。

差分对设计:保持差分线长度一致(误差≤50mil),间距恒定(如5mil),以抑制共模噪声。

阻抗控制:通过叠层设计(如调整介质厚度、铜箔厚度)实现阻抗匹配(如单端50Ω、差分100Ω)。

电源与地设计

电源分割:多电源系统需分割电源层,通过磁珠或0Ω电阻隔离,避免噪声耦合。

地平面完整性:优先保证完整地平面,减少地弹效应;高频信号采用多点接地,低频信号单点接地。

去耦电容布局:在电源引脚附近放置去耦电容(如0.1μF+10μF组合),缩短回流路径。

二、材料选择:匹配高频特性需求

基板材料

低损耗材料:选用介电常数(Dk)稳定、介电损耗(Df)低的材料(如Rogers 4350B、Taconic TLX系列),减少信号衰减。

热膨胀系数(CTE)匹配:确保基板与铜箔CTE接近,避免高温下分层。

铜箔与表面处理

铜箔类型:采用低轮廓铜箔(HVLP),减少趋肤效应对高频信号的影响。

表面处理:沉金(ENIG)或化学镍钯金(ENEPIG)提供平整表面,适合高频信号传输;避免喷锡(HASL)因表面粗糙度导致阻抗不连续。

三、制造工艺:保障精度与可靠性

制版与蚀刻

激光直接成像(LDI):提高线路精度(线宽/间距误差≤±10%),减少菲林对位误差。

蚀刻补偿:根据蚀刻因子调整线路设计,确保实际线宽符合要求。

钻孔与孔金属化

激光钻孔:用于微孔(≤0.1mm)加工,提高孔壁光滑度。

沉铜与电镀:控制沉铜厚度(≥1μm),确保孔铜均匀性(≥20μm),避免孔断。

层压与阻抗控制

真空层压:减少层间气泡,提高叠层结合力。

阻抗测试:使用TDR(时域反射仪)验证阻抗一致性,偏差≤±10%。

四、测试与验证:全面评估性能

电气性能测试

信号完整性测试:通过眼图、抖动、插入损耗等指标评估高速信号质量。

阻抗测试:验证单端/差分阻抗是否符合设计要求。

串扰测试:测量相邻信号间的耦合噪声,确保串扰≤-40dB。

环境可靠性测试

热循环测试:模拟温度变化(如-40℃~125℃),检查焊点可靠性。

振动测试:验证机械结构在振动环境下的稳定性。

ESD测试:确保PCB满足IEC 61000-4-2标准(如±8kV接触放电)。

五、沟通与协作:确保需求精准落地

与厂商技术对接

提供完整设计文件:包括Gerber文件、BOM清单、钻孔文件、叠层结构说明。

明确工艺要求:如阻抗控制、表面处理、孔径公差(通常±0.05mm)。

选择专业厂商:优先选择有高速PCB打样经验的厂商,确保工艺能力匹配。

样品评估与反馈

外观检查:检查板面平整度、阻焊覆盖、字符清晰度。

功能测试:装配元器件后进行实际功能验证,记录问题点。

迭代优化:根据测试结果调整设计或工艺,直至满足要求。

六、成本控制与交期管理

合理规划打样数量:根据测试需求确定数量(如5-10片),避免浪费。

选择加急服务:紧急项目可选用厂商加急服务。

优化设计减少成本:如合并拼板、简化工艺(如减少盲埋孔),降低打样费用。

关于高速PCB打样需要注意哪些事项?高速PCB打样需要注意事项的知识点,想要了解更多的,可关注领卓PCBA,如有需要了解更多PCBA打样、PCBA代工、PCBA加工的相关技术知识,欢迎留言获取!